# Advanced Packaging Technologies Update

Welcome to ASM Pacific Technology Limited

www.asmpacific.com

# **Presentation outline**

- Advance Packaging Technologies driving forces

- New trend in WLCSP (Mold Protected WLCSP)

- Advance FC interconnect Technologies

- Various FanOut Technologies

- FanOut Process and material consideration

# Advance Packaging Technologies Driving Forces ASM

| <image/> <section-header><section-header><section-header><section-header><section-header></section-header></section-header></section-header></section-header></section-header> |                                                                                    | Mobile/Tablet                                                                           | IOT<br>Big Data                                                                                                                                                                                                                                                      |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                |                                                                                    | Low cost but hi vol.<br>High Performance<br>Miniaturization<br>Low power<br>consumption | <ul> <li>Lower cost but higher vol.</li> <li>Mid &amp; High Performance</li> <li>High speed connection</li> <li>Miniaturization</li> <li>Low power consumption</li> <li>Fab-like technology</li> <li>Embedding technology</li> <li>Fusion/combo structure</li> </ul> |  |

| Integration                                                                                                                                                                    | SoC                                                                                | SoC / SiP                                                                               | Advanced SiP                                                                                                                                                                                                                                                         |  |

| Products                                                                                                                                                                       | cts Wireless / AP / PMIC / RF / Wireless / RF / Wireless / Memory / Touch IC / CIS |                                                                                         | AP/ Micro processor / PMIC /<br>RF / Wireless / Memory /<br>CIS, MEMS & Sensors                                                                                                                                                                                      |  |

| <b>Format</b><br>3/14/2017                                                                                                                                                     | Singulated,<br>Low density strip                                                   | Strip Block Matrix                                                                      | Hi density strip block matrix,<br>Wafer, and Panel form                                                                                                                                                                                                              |  |

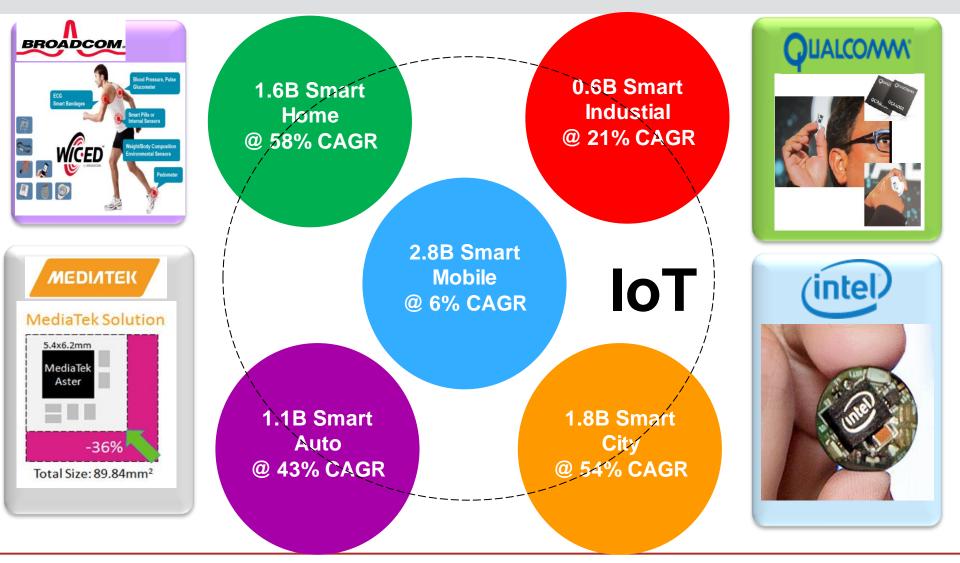

#### Explosive growth expected for IoT by 2020 Expected number if IoT device to be shipped in 2020

# New trend in WLCSP for both IC & Discrete

Welcome to ASM Pacific Technology Limited

www.asmpacific.com

# **Wafer Level Packages**

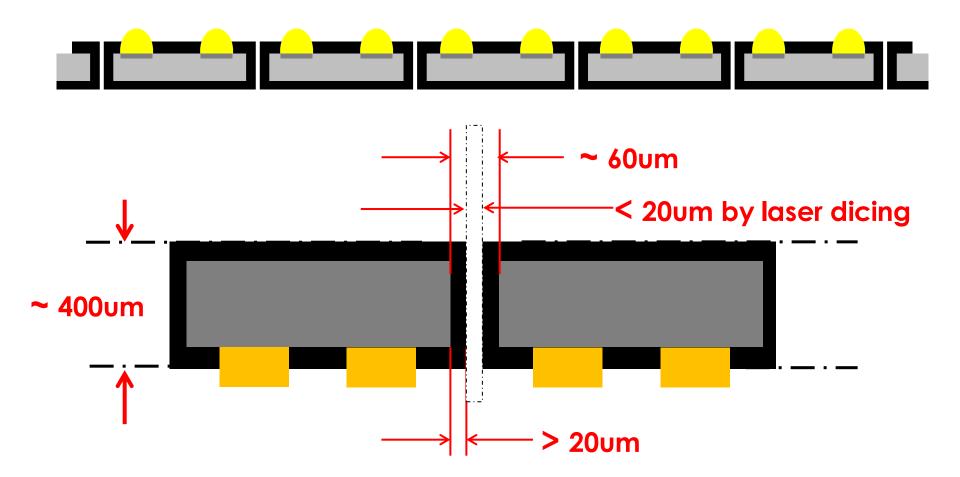

## **Mold Protected WLCSP**

# Mold Protected (mpWLCSP) Solution

ASM 🖄

# Advance Interconnect Technologies

Welcome to ASM Pacific Technology Limited

www.asmpacific.com

# **Advance FC Interconnect Model**

- ~ 40 um pitch, micro pillar bump

- 2.5D Si/Glass Interposer

- for multi-die (Die partition & Heterointegration)

- MR & TCB (Fluxless TC LPC, TCCUF, TCNCP)

C2S, C2W

Source: Xilinx.

- 10 to 40um pitch

- U pillar bump

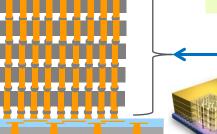

- 3D TSV Dies Stacking w/ TC Bonding (FluxLess TC LPC, TC NCF)

C2C2S, C2C2W

Bottom Die

8+1 Stacked TSV Thin Die by Thermal Compression Bonding

- 50um to 130um pitch

- C2 (Cu Pillar) & C4 bump tech.

- <u>MR & TCB</u> (TC LPC, TCCUF & TCNCP)

HD BuildUp substrate, Multilayers laminate, <u>MIS</u>, & L/F

C2S, C2P

#### Advanced BGA Packaging Enabling Small, Thin Designs

Intel<sup>®</sup> Core<sup>™</sup> M

Processor

30 X 16.5 X 1.05mm

495 mm<sup>2</sup>

40 X 24 X 1.5mm

960 mm<sup>2</sup>

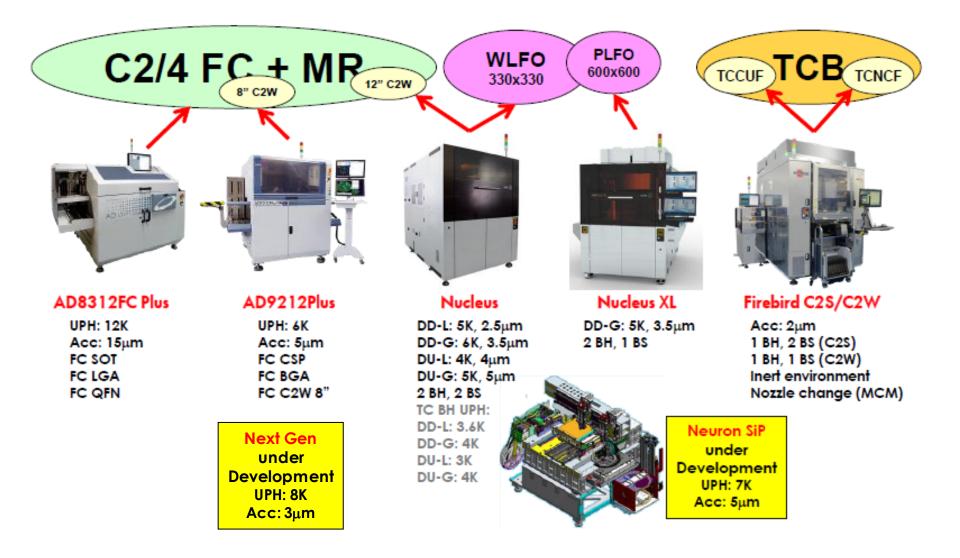

#### ASM Advanced Packaging Total Solution

| Key   | / Features           | AD8312FC     | AD9212+                 | Firebird S              | Firebird W                       | Nucleus                             | Nucleus XL                    |  |  |

|-------|----------------------|--------------|-------------------------|-------------------------|----------------------------------|-------------------------------------|-------------------------------|--|--|

| Αςςι  | uracy @3σ            | ±10um        | ±5um                    | ±2um                    | ±2um                             | ±2.5um (Local FC)                   | +/-5um (Global FC)            |  |  |

| Align | ment Mode            | Local        | Local                   | Local                   | Local                            | Local & Global                      | Local & Global                |  |  |

| Place | ment Mode            | DA & FC      | FC                      | FC                      | FC                               | DA & FC                             | DA & FC                       |  |  |

| Max.  | Bond Force           | 30N          | 15N                     | 30N                     | 30N                              | 300N                                | 30N                           |  |  |

|       | nd Collet<br>Heating | -            | -                       | Pulse, 400°C<br>max     | Pulse,<br>400°C max              | Const,350°C max                     | Const, 200C max,<br>Optional  |  |  |

| Stag  | ge Heating           | -            | -                       | 200°C max               | 200°C max                        | 250°C max                           | -                             |  |  |

| Max   | x. strip size        | 100x300 mm   | 210x323 mm              | 125x250 mm              | 300 mm Ø                         | 300 mm ø,<br>340x340 mm             | 670x600 mm                    |  |  |

|       | C2W                  | -            | 8″                      | - Upto 12" U            |                                  | Upto 12"                            | -                             |  |  |

| C     | Die Size             | 0.25 – 10mm² | 0.5 – 30mm <sup>2</sup> | 2x2 –<br>33x22mm²       | 2x2 –<br>33x22mm²                | 0.5 – 25mm <sup>2</sup>             | 0.5 – 25mm <sup>2</sup>       |  |  |

| Die   | Thickness            | 50um         | 50um                    | 50um                    | 50um                             | 50um                                | 50um                          |  |  |

|       | Fluxer               | $\checkmark$ | $\checkmark$            | Opt                     | Opt                              | Opt.                                | Opt.                          |  |  |

| Di    | ispenser             | Opt. (Dual)  | -                       | -                       | -                                | -                                   | -                             |  |  |

| М     | lultichip            | -            | -                       | ✓ TnR                   | ✓ TnR                            | ✓ Multi-die ejector                 | ✓ Multi-die ejector           |  |  |

| С     | Class100             | -            | -                       | $\checkmark$            | $\checkmark$                     | $\checkmark$                        | $\checkmark$                  |  |  |

| Тар   | pe & Reel            |              |                         | $\checkmark$            |                                  | -                                   | -                             |  |  |

| Ар    | plication            | FCOL         | C2W, FCCSP,<br>FCBGA    | C2S TCCUF,<br>2.5D & 3D | C2W TCCUF,<br>TCNCF<br>2.5D & 3D | 2.5D, FOWLP/PLP,<br>Active Embedded | 2.5D, PLP,<br>Active Embedded |  |  |

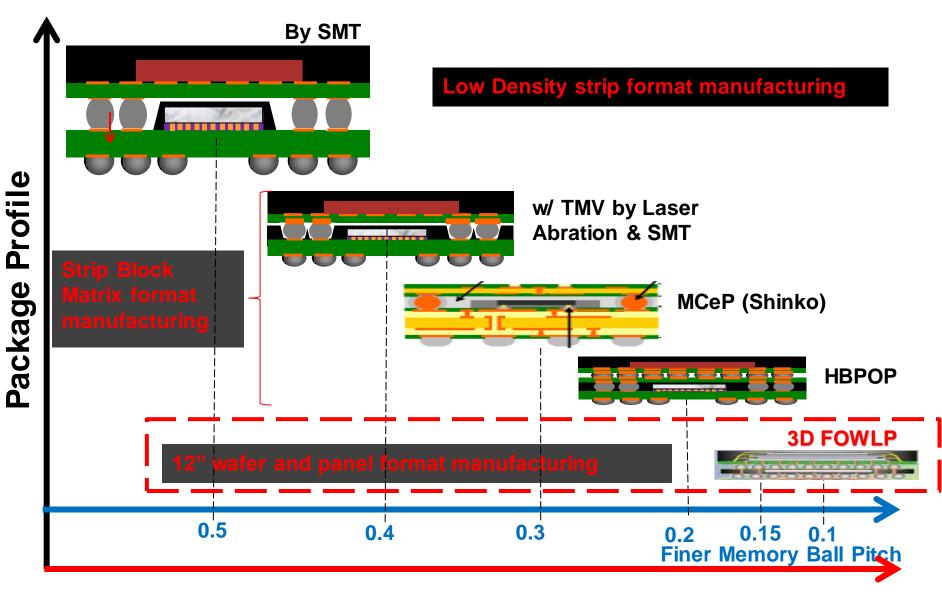

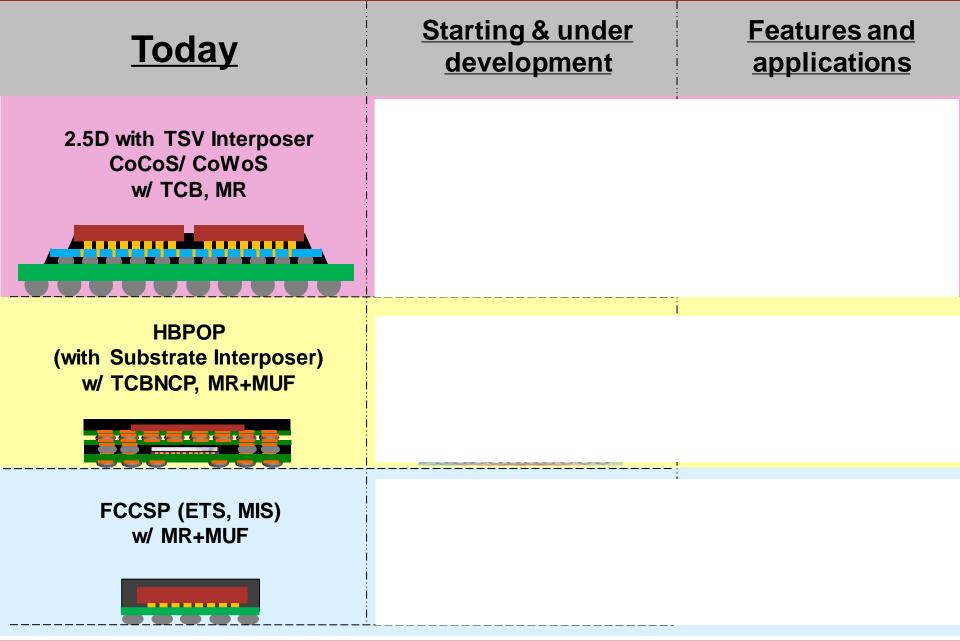

# **AP POP Evolution Trend**

#### Higher Memory BGA I/Os for higher band width communication

# Various FanOut Technologies as the alternatives

**ASLAC: Accuracy, Speed & Large Area Capability**

Welcome to ASM Pacific Technology Limited

www.asmpacific.com

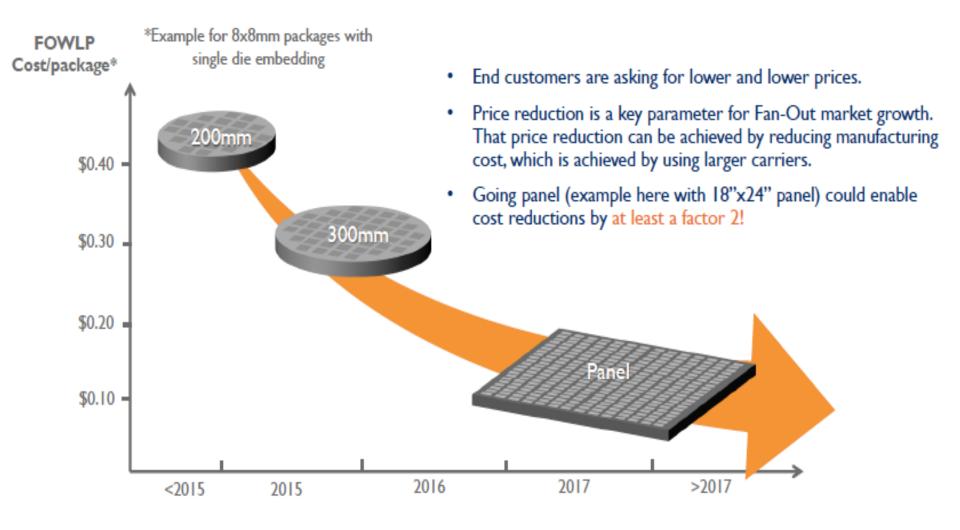

# eWLB (embedded Wafer Level BGA by Infineon)

## **Process:**

- 12" wafer format

- Low density RDL

- Die 1<sup>st</sup>, Die Down, Global Alignment

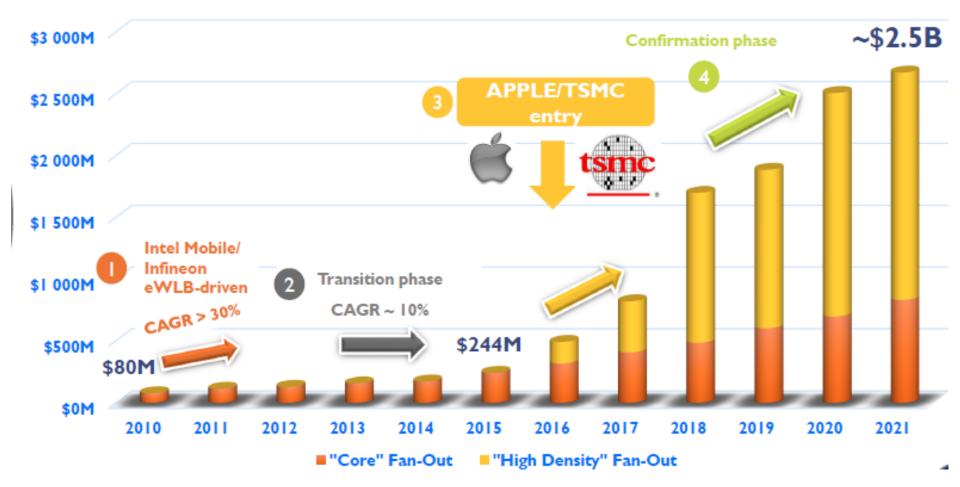

#### Fan-Out activity revenues forecast (M\$) Breakdown by Fan-Out market type

## **Taking off of Fan Out Technologies**

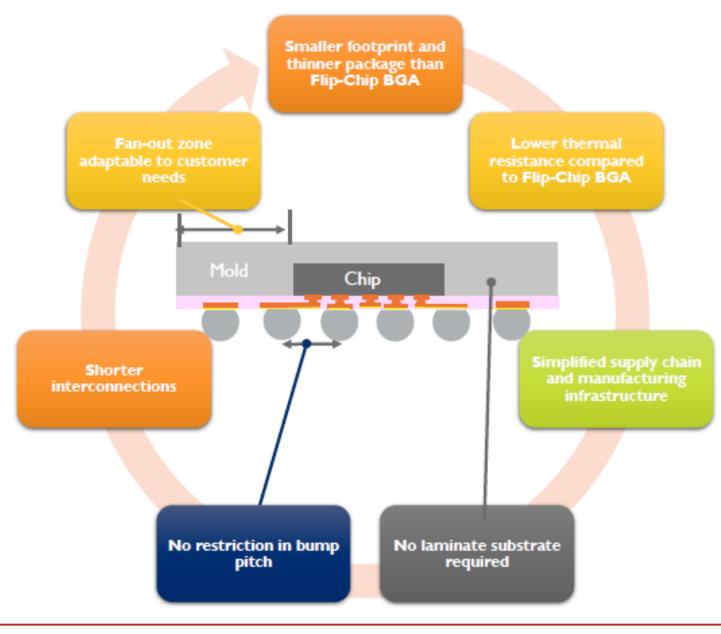

## **The Power of Fanout Technologies**

# Process and Material consideration for Fanout Technologies

#### **ASLAC: Accuracy, Speed & Large Area Capability**

Welcome to ASM Pacific Technology Limited

www.asmpacific.com

## eWLB Advantages

- Better 2<sup>nd</sup> level reliability than WLCSP

- Excellent electrical performance

- RoHS & REACH compliant

- Low profile, miniaturized high performance package

- No substrate, no bump, no flux no reflow, no underfill

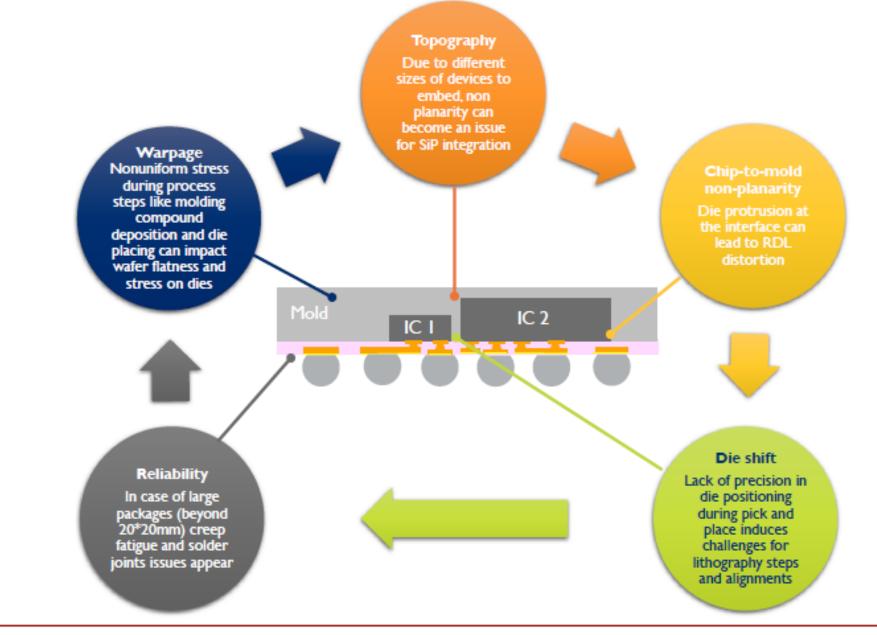

## **Technical Challenges**

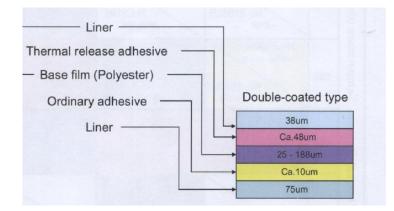

#### **Adhesive Film for Die Down Attach**

- Thermal release tape

- Chip first (Die down) structure

- Temporary bonding

- Good adhesion during molding

- Easy release at a higher temperature

- Thickness: 100 150 um

- Lamination on the carrier

#### Revalpha from Nitto Denko

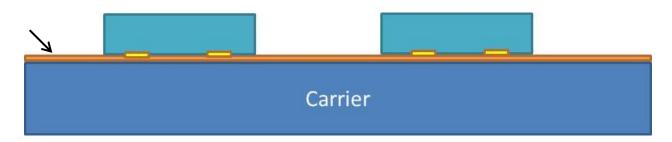

#### Adhesive Films for Die up Attach

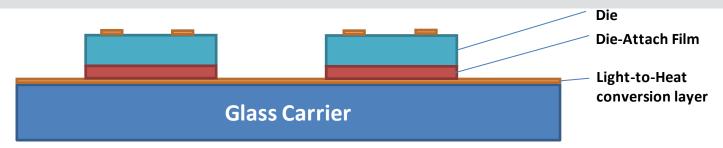

- DAF and LHTC

- Chip first (Die up) structure

- Die Attach Film (DAF) Thickness: 15 25 um

- A Light to Heat Conversion Layer (LTHC): a sacrificial layer for debonding

- Compatible with typical semiconductor chemistries and processes

- Excellent adhesion

- Low modulus, High Tg, thermal stable at subsequent RDL process

| DAF     | Тд   | Elastic<br>Modulus<br>(150C) | Bonding<br>temperature | Bonding<br>Pressure |

|---------|------|------------------------------|------------------------|---------------------|

| Hitachi | 180C | 6 MPa                        | 100 -160C              | 0.05 -0.2 Mpa       |

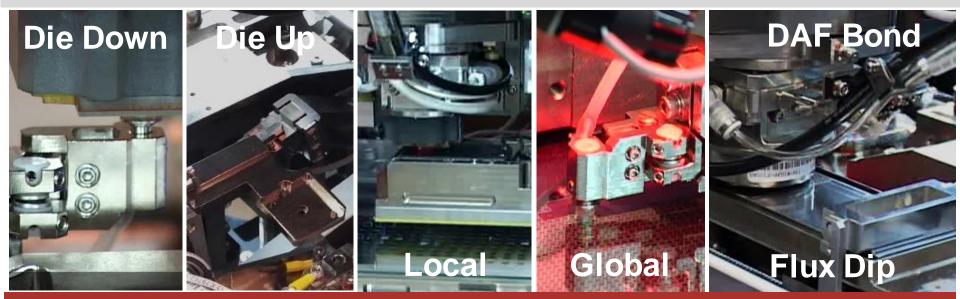

### **Pick and Place Die Attach Process**

#### Many different process approaches with the same manufacturing format

- Chip 1<sup>st</sup> / RDL 1<sup>st</sup> (Global / Local alignment)

- Die down / Die up

- Flux dipping for high accuracy C2W FC process

- High bond force with elevated bond temperature for DAF bonding

- Compensation for die shift

#### Accuracy Performance NUCLEUS Placement Accuracy to Support Different Process Need

|        | Flip Chip       | Local<br>Alignment  | +/- 2.5um |

|--------|-----------------|---------------------|-----------|

|        | (Die Down Mode) | Global<br>Alignment | +/- 3.5um |

| 30 100 | Die Bond        | Local<br>Alignment  | +/- 4um   |

|        | (Die Up Mode)   | Global<br>Alignment | +/- 5um   |

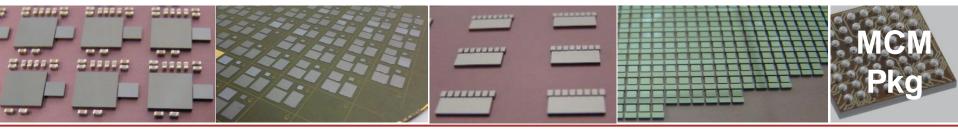

## MCM Process Capability

Automatic Collet and Ejector Tool Change

#### Automatic Bond Collet Tool Change

- Automatically change bond collet tools for different die size in MCM pkg

- Support 4 5x different die size collet tool change

#### Multiple Die Ejector System

- Automatic changer for die ejector

- Support up to 5 different types of ejector kit installation

- Synchronize needle motion with bond head and flipper

- Support die size up to 30mm

3/14/2017

#### **Flexible Process capability**

Thermal Compression Bond Head and Light Bond Head

Thermal Compression Bond Head (Ready)

- Bond force: 10 300N Bond force accuracy: < 40N: ±2N

- > 40N: ± 5%

- Collet Heating: 350°C Heating mode: Continuous Bond head rotation of ±15° for fine bond accuracy adjustment

Light Bond Head (To be available in Q3)

- Bond force: 0.5 10N Bond force accuracy:

- < 2N: ±0.1N

- > 2N: ± 5%

Bond head rotation of ±15° for fine accuracy adjustment

C

AoA

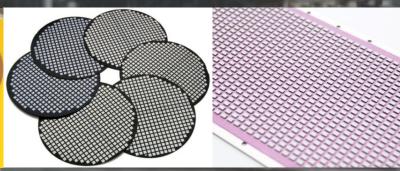

#### Suitable for Different Format

Large Format Handling – Round and Quad

Large Work Holder Design

- To support up to

- 12" Wafer Substrate / Carrier

- 330 x 330mm<sup>2</sup> Panel Substrate / Carrier

- 12" wafer with auto load/unload

- Support Work Stage heating up to 250°C

- Integrated equipment solution for FOWLP, FOPLP and Active Embedding

#### **Multiple Material Handling System Configurations**

**Compatible with Different Material Format**

#### **EMC** Materials for FOWLP

Sheet/B-stage

Liquid (automation)

**Granular (automation)**

|           |                    | Thinne<br>Packag |              | Product performance |                                    | Productivity |                | Cost-effective |                      | Scalability     |       |                 |  |

|-----------|--------------------|------------------|--------------|---------------------|------------------------------------|--------------|----------------|----------------|----------------------|-----------------|-------|-----------------|--|

| Sheet +++ |                    | +++++            | •            | +++++               |                                    |              | +++            |                | ++                   |                 | +++++ |                 |  |

| Liqui     | id                 | ++++             |              | -                   | ++++                               |              | +++            |                | +++                  |                 | ++++  |                 |  |

| Granu     | ılar               | +++              |              | ++++                |                                    | +++          |                | +++++          |                      | +++             |       |                 |  |

|           | Nagase (R4507)     |                  | ler con<br>) | tent                | Filler size<br>(average/max<br>um) | (            | CTE<br>(ppm/C) |                | ıng's<br>dulus (GPa) | IMC<br>(OC/min) |       | PMC<br>(oC/min) |  |

| Ν         |                    |                  |              |                     | 8/25                               |              | 10             | 19             |                      | 125/10          |       | 150/60          |  |

|           | Sumitomo<br>(G730) | 90               |              |                     | 55                                 |              | 7              | 30             |                      | 125/10          |       | 150/60          |  |

#### **Technical Challenges for Compression Molding**

- Die Shift

- Molding Process optimization

- Dispensing

- In particular thin mold cap of less than 100  $\mu$ m

- Moldability

- Co-planarity TTV of 20  $\mu$ m get more challenging with increase size

- Flow mark due to dispensing limitation for thin mold cap and material formulation

- Incomplete fill due to poor process optimization and low vacuum level

- Mold Bleed on die due to de-bonding of thermal tape

- Film wrinkle is translated on the molded panel or wafer due to larger size, as maintaining tautness of film during compression is challenging

- Warpage Control

- EMC with low CTE and low modulus

- CTE Matching between EMC, adhesive films and carrier materials

#### Warpage being the Major Challenge

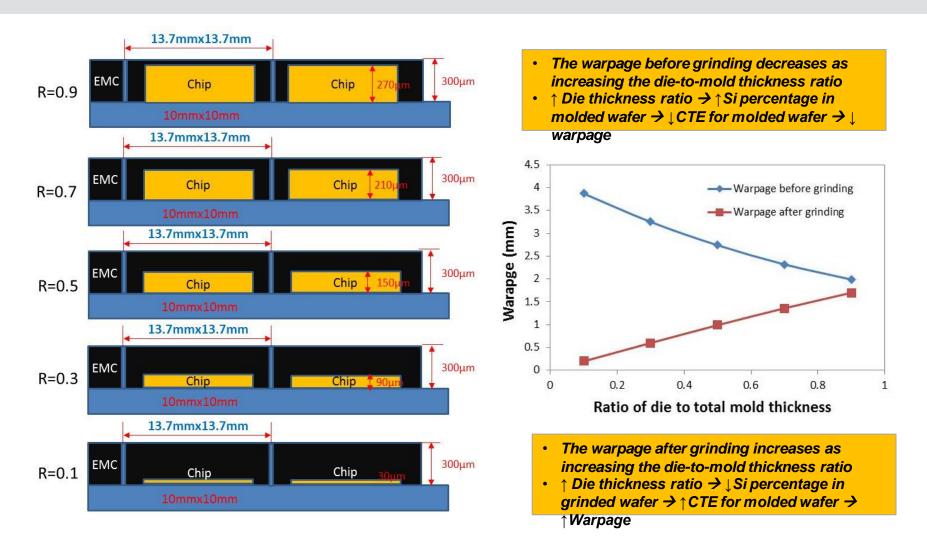

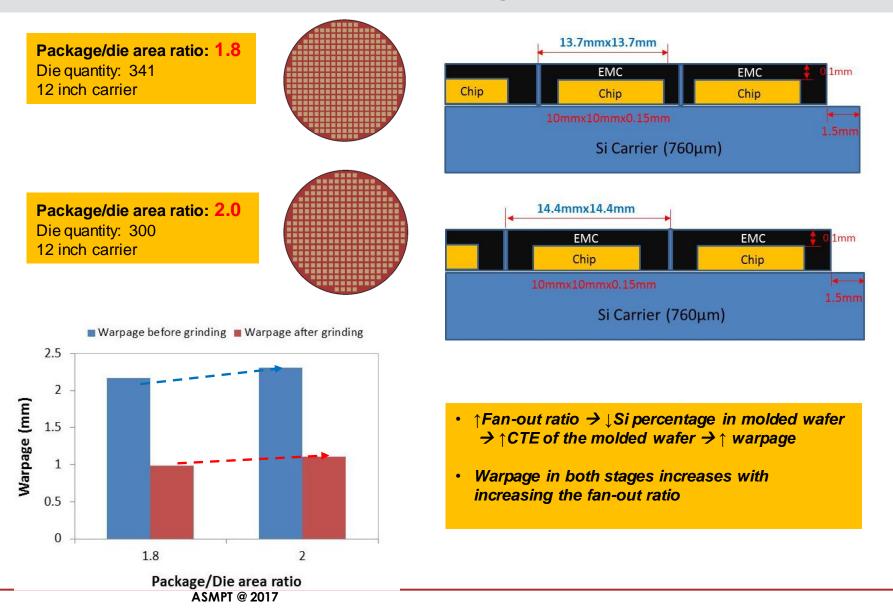

#### Package Design

- Volume ratio of die to EMC

- Die/Package thickness

- Die to package fan-out ratio

- Material Selection

- EMC

- CTE, Modulus

- Temporary carrier

- CTE, Young's modulus

- Adhesive

- Young's modulus, thickness

- Process optimization

- Bond force

- Temperature

#### **Effect of Die Thickness on Warpage**

#### Effect of Fan-out Area Ratio on Warpage

## "ASLAC" for WLP & PLP (2.5D & 3D)

# ASLAC =

Accuracy

(2.5 um to 10um)

# **S**peed

+

(5k to 25k uph)

# + Large Area Capability

(300 Ø to 600x600 mm)

## "ASLAC" for WLP & PLP (2.5D & 3D)

# **Together We Can**

ASM Pacific Technology Innovation and Technology Leader