### Build China's IC Ecosystem Forum - Advanced Manufacturing, Assembly & Test

## Innovative 3D-SiP Package Technologies for More than Moore Era

Excel as World Class Leading Provider of Assembly and Test

15/Mar-2017

## **Outline**

Packaging Trend of SMART Phone/ Wearable/ Networking Devices

◆ Innovative 3D-SiP Packaging Technologies

Summary

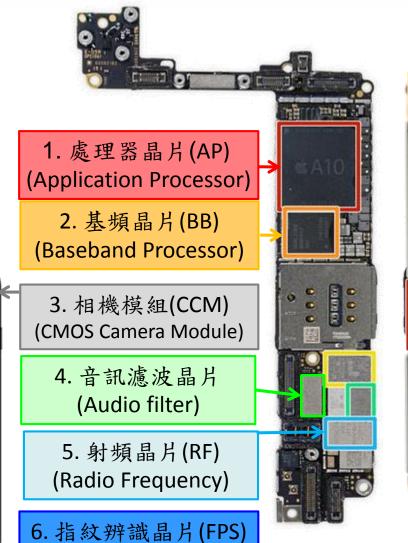

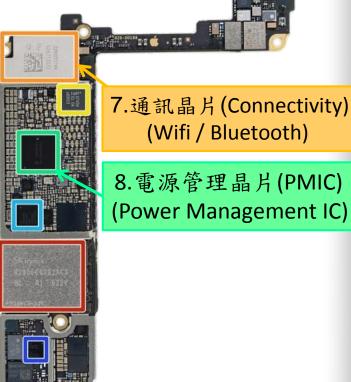

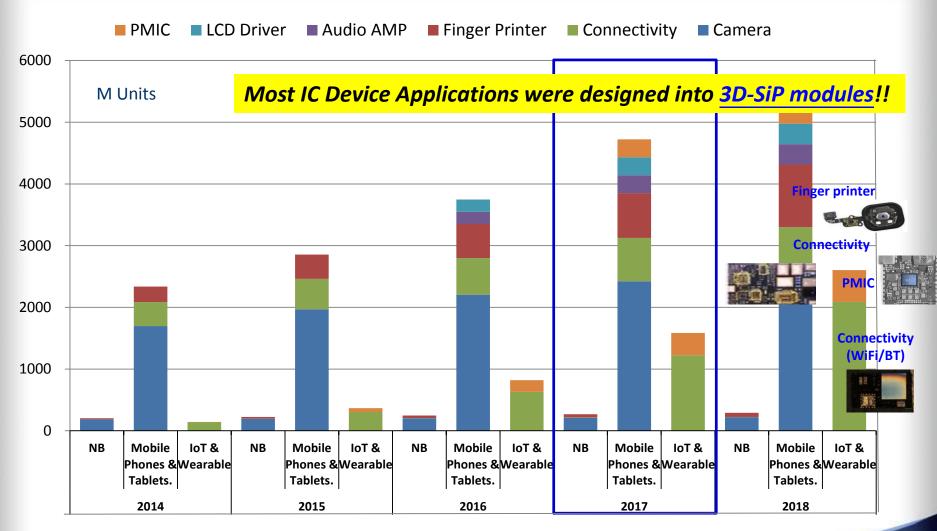

## IC Device Applications in Mobile

(Finger Print Sensor)

## **3D-SiP** Market Growth Rate Overview

Source: Gartner, Morgan Stanley, Market Information

# Innovative 3D-SiP Package Technologies

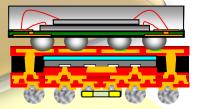

**I. SiP TECHs**

# Innovative 3D-SiP Package Solutions

# **3D-SiP** Benefits & Challenges

#### **Application:**

WiFi/ BT/ NFC / GPS / FM Module Development

#### Benefits:

SiP can provide the *small form factor*, *low cost* and *multi-function*

integration solutions.

#### Challenges:

Some KEY technologies are needed to develop ASAP !!!

- 1. EMI shielding

- 2. Antenna on PCB

- 3. Die on passive component

- 4. IPD/Die embedded in PCB

## **3D-SiP** Miniaturization Tech Solutions

**75%** size reduction

MCU + WiFi COB Solution

MCU + WiFi SiP solution

Size: 22x19mm

Size: 10x10mm

- Include WiFi + MCU

- Component Count : 50

- Process: wafer thinning, stack Die on FC, MUF, EMI Coating

MCU + BLE COB Solution

Size: 18x12mm

MCU + BLE SiP solution

Size: 6.5x6.5mm

- Include BLE, Flash, X'tal, Antenna

- Component Count: 28

- Process: Stack die on Passives, Antenna in Package, Compress Molding

WiFi Plug

WiFi Bulb

**Hand Band**

## Innovative PKG Technologies for 3D-SiP

**SPIL Leading**

#### 1. Embedded Actives

> Small PKG Size/Height

#### 2. Embedded Passives

- Lower PKG Z Ht /

- Lower Power Consumption

- Low EMI Noise

#### 3.Two side PKG

- ➤ High Yield /

- ➤ High Integration

#### 7. Antenna in SiP

> Small PKG Size

# Its Happer Now !!

#### ภาบ on Die (F2F)

**Electrical Performance**

#### 6.Partition MI

Small Form Factor/ High Integration

#### 5.Die on CAP

> Small PKG Size

## **3D-SiP** New Package TECH. Trend

$(CAGR \rightarrow 39.3\% / 55.8\%)$

## **Antenna in SiP**

2 Side SiP

- 1. High function Integration

- 2. Small form Profile Performance

## **Partition EMI**

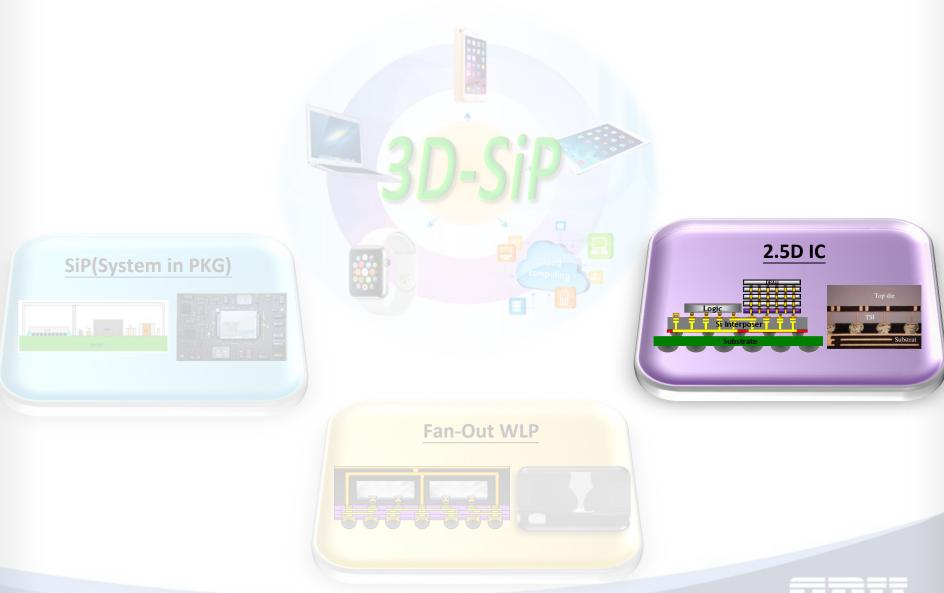

# Innovative 3D-SiP Package Solutions

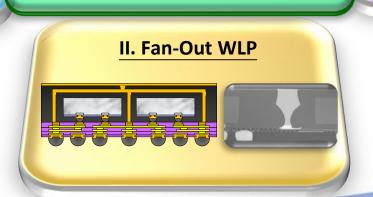

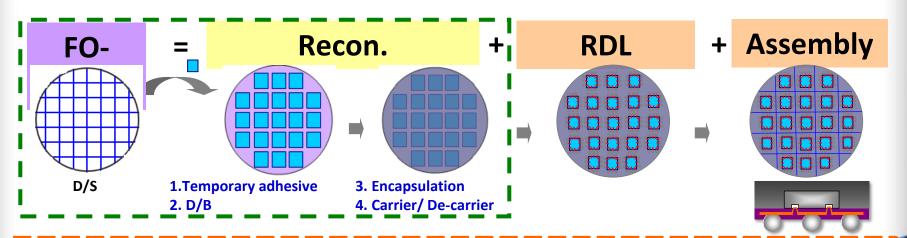

## FO-WLP PKG Category & Its Product Applications

|                    | I/O<br>Density     | RDL<br>L/S(um) | PKG Solution              | Application                                                                          |  |  |  |

|--------------------|--------------------|----------------|---------------------------|--------------------------------------------------------------------------------------|--|--|--|

| \$ <mark>G1</mark> | Z<br>Ultra<br>High | 0.1<br>↓<br>2  | FO-MCM Silicon Interposer | Networking Application:  1. High performance computing 2. Networking 3. Data servers |  |  |  |

| G2<br>W            | High               | 2<br>↓<br>10   | FO-PoP HBW-PoP            | Mobile Application: 1. Smart Phone & Tablet 2. High End AP/BB                        |  |  |  |

| G3                 |                    | >10            | FO-SD FC-ETS              | Mobile Application: 1. Low Pin Count 2. PMIC/RF/PA                                   |  |  |  |

| M<br>G4<br>W       | <b>M</b> iddle     | variability    | FO-SIP SIP Module         | IoT/Wearable Application: 1. Connectivity module 2. PMIC Module                      |  |  |  |

> FO technology to fulfill potential product applications.

# Why Fan-Out WLP Technology?

### **Application:**

Keep sufficient area for PCB board I/O as the die size shrinking (28/20/16nm), application for Mobile AP/ Baseband/ PMIC and HDD/SSD Controller.

2sides RDL FO-PoP

**MCM-FOWLP**

### Benefits:

- ✓ <u>Small form factor & thinner package (substrate-less).</u>

- ✓ <u>High IO/High bandwidth with fine line/multi-layer RDL routiability.</u> (Line/Space = <10um, >2L RDL layer)

Challenges: Wafer Warpage & Poor BLR (Board Level Reliability)

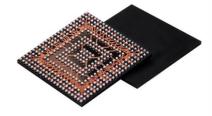

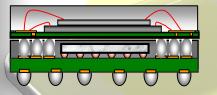

## 3D-SiP Package Apply for AP/BB in Smart Phone

### ePoP & BD-PoP

PKG THK: 1.2~1.5mm

PKG THK: 1.2mm

## **HWB-PoP & FO-PoP**

(High Bandwidth)

NOW!!

Next

Generation!!

PKG THK: <1.1mm

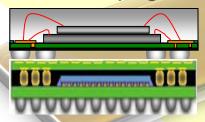

## FO-PoP+FO-MCM

(Ultra Thin Profile)

PKG THK < 1mm

## **Benefit:**

- 1. High Electric & Thermal Performance

- 2. Ultra thin Profile Performance

(Z ht < 0.5mm)

# Innovative 3D-SiP Package Solutions

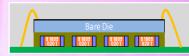

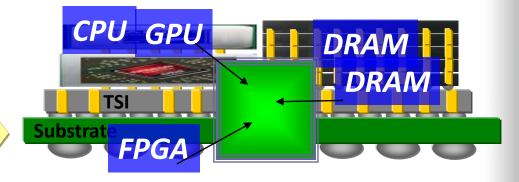

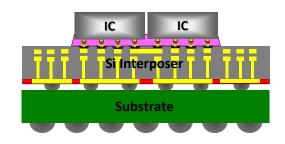

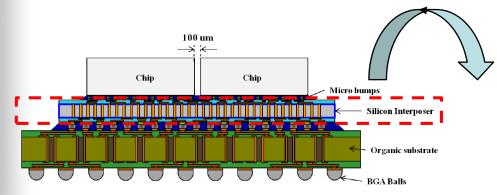

# Why 2.5DIC Technology?

### The Trend of Future!

- ✓ Heterogeneous integration

- √ Smaller PKG size

- ✓ Higher performance

Al Market (deep learning, supercomputer)

# **OSAT Role in 2.5DIC Supply Chain**

| Process | FEoL     |              | MEoL                    |                        | BEoL             |                           |      |

|---------|----------|--------------|-------------------------|------------------------|------------------|---------------------------|------|

| Model   | Logic IC | TSV + FS RDL | Front-side<br>Micro-pad | Backside<br>Via Reveal | BS RDL<br>+ Bump | Micro Joint &<br>Assembly | Test |

| 2.5D    | IC Fab   |              | SPIL                    |                        |                  |                           |      |

| 3D      | IC Fab   |              | SPIL                    |                        |                  |                           |      |

- Enabling technologies development for 2.5DIC MEoL and BEoL capability.

Same capability capable for 3DIC.

- For TSV Silicon Interposer (TSI), OSAT collaborate with wafer foundries

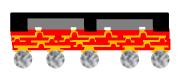

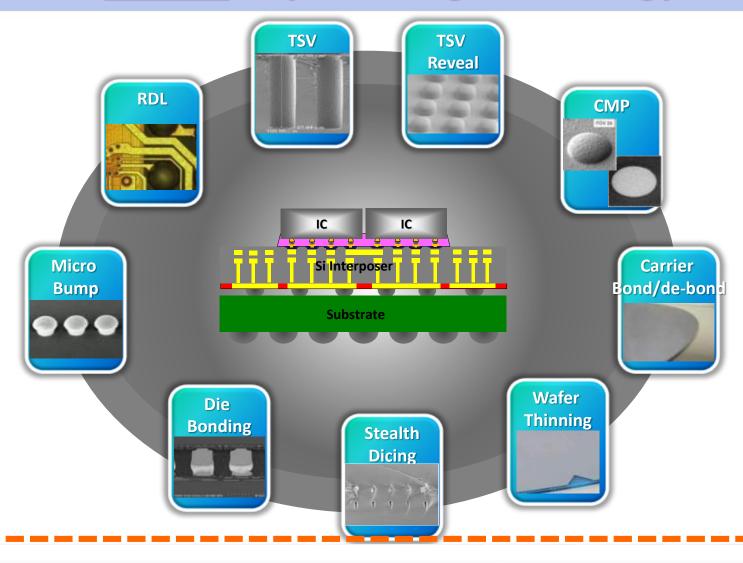

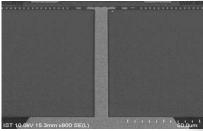

# **2.5DIC** Key Enabling Technology

Challenges: Wafer Warpage & Poor PLR(Package Level Reliability)

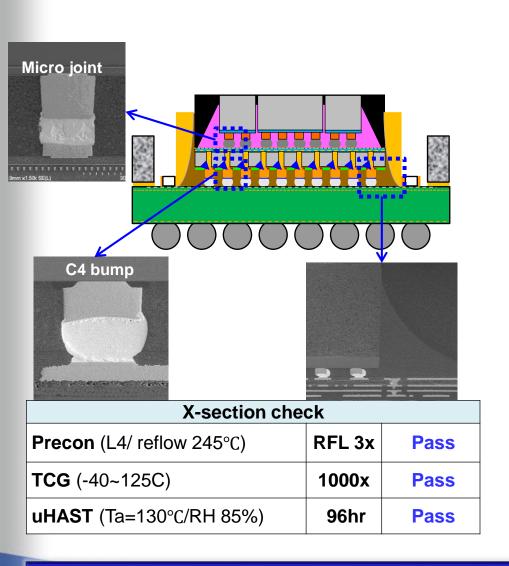

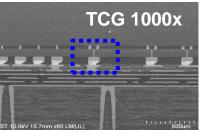

# 2.5D Packaging Readiness

- √ No abnormal was observed on C4 bump joint , UF dispense and adhesive process

- √ 1 ASIC +4HBM structure passed L4 + TCG1000

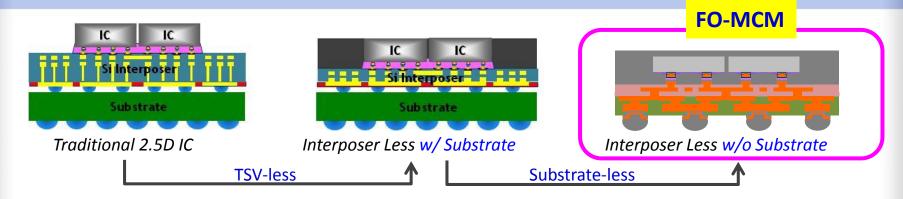

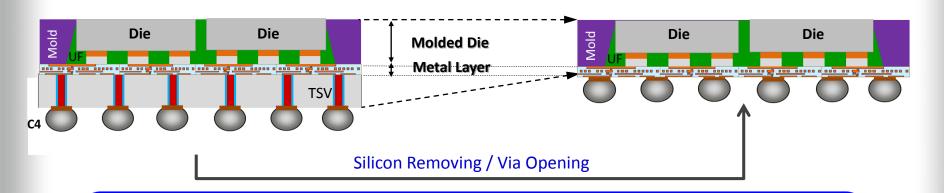

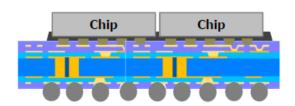

### FO-MCM (w/o Si Interposer) - Low Cost Alternatives of 2.5D

- ✓ Merits of 2.5D IC to FO-MCM Platform

- Shortening interconnection distance high speed & bandwidth performance.

- Reducing interposer cost due to excluding TSV related process cost.

- Processing by all existing MEoL/BEoL equipments.

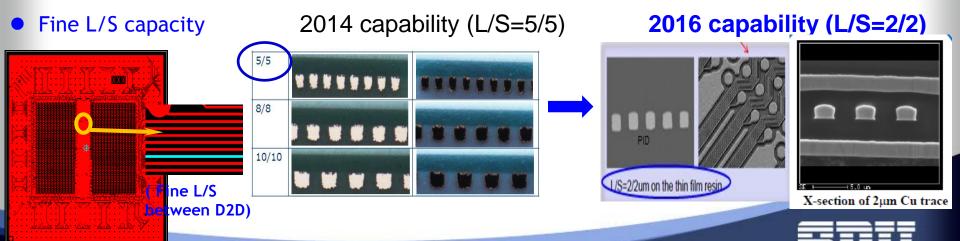

### 2.1D (by Substrate) - Low Cost Alternatives of 2.5D

Organic Interposer: (w/ core)

- Organic Substrate replace Si interposer as interface between die & substrate.

- Characteristic:

- Fine pitch: trace L/S  $>> 10/10 \rightarrow 2/2um$

## **Outline**

Packaging Trend of SMART Phone/Wearable/

Networking Devices

Innovative 3D-SiP Packaging Technologies

Summary

## **Conclusion**

- New Package TECHs Focuse on Three 3D-SiP

- **System in Package** (w/ 7 miniaturization TECH)

- Fan-Out Wafer Level Package (Substrate-less; for thin & small form factor)

- 2.5DIC PKG (w/ Low Cost PKG solutions; such as 2.1D Substrate)

# Solution Providing Innovative Leader

Destroyed to 1836

Being your preferred solution provider

Advanced Wire Bond Large Flip Chip Pacl

SPIL New Plant

Big Area More than Turnkey Service Bump Advance Package Line 3DIC,

For more:www.spil.com.tw

**Contact Information:**

albertlan@spil.com.tw